# Sixth Semester B.E. Degree Examination, July/August 2021 Digital Communication

Time: 3 hrs.

Max. Marks:80

Note: Answer any FIVE full questions.

- 1 a. Define the pre-envelope. Show the spectral representation of pre-envelopes for low pass signal. (06 Marks)

- b. Define Hilbert transform. State and prove its properties.

(06 Marks)

- c. For the binary data 10011101, sketch the following

i) RZ unipoler

- ii) NRZ polar

- iii) NRZ Bipolar

- iv) Manchester format.

(04 Marks)

- 2 a. Derive the expression for power spectral density of polar signaling. (08 Marks)

- b. Derive the expression for complex low pass representation of band pass system. (08 Marks)

- 3 a. Explain the geometric representation of the signal for N = 2 and M = 3 and explain the various parameters. (06 Marks)

- b. S.T. correlator outputs are statically independent,

(04 Marks)

- c. What do you mean by match filter receiver? Derive the expression for the impulse response of matched filter receiver. (06 Marks)

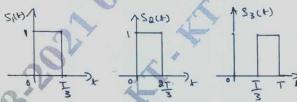

- 4 a. Using Gram-Schmitt orthoganalization procedure and find the orthnormal basis function for the signal shown below.

Fig.Q4(a)

(08 Marks)

- b. With neat block diagram explain detector and maximum likelihood decoder of a correlation receiver. (08 Marks)

- 5 a. Explain the generation and detection of BFSK.

(06 Marks)

- b. With the signal space representation of BPSK derive the expression for probability of error.

(06 Marks)

- c. For the input binary sequence 11001001, draw the in phase and quadrature phase components of the QPSK signal. (04 Marks)

- 6 a. With a neat block diagram, explain the generation and coherent detection of QPSK signal.

(06 Marks)

- (0)

- b. Explain the DPSK transmitter and receiver with neat block diagram.

(06 Marks)

c. Explain the binary FSK using non coherent detection.

(04 Marks)

- With a neat diagram of digital PAM system obtain the expression for ISI. (10 Marks) (06 Marks) State and prove Nquist criterion for zero ISI. Explain the design by band limited signals with controlled ISI. (10 Marks) With neat diagram and relevant expressions explain the concept of adaptive equalization. (06 Marks) Explain the model of a spread spectrum digital communication system. (08 Marks) A slow frequency Happed/MFSK system has the following parameters i) The number of bits/MFSK symbol = 4 ii) The number of MFSK symbol per hop = 5 iii)Calculate the processing gain of the system in decibels. (02 Marks) List and briefly explain any 3 application of direct sequence spread spectrum. (06 Marks)

- a. With a neat block diagram explain frequency spread spectrum technique. Also explain the terms chiprate, jamming margin and processing gain. (08 Marks)

b. Explain the effect of dispreading on a narrow band interference in direct sequence spread spectrum systems.

A DSSS signal in designed to have the power ratio  $P_R/P_N$  at the intended receiver is  $10^{-2}$ . If the desired  $E_b/N_0 = 10$  for acceptable performance. Determine the minimum value of processing gain. (08 Marks)

# CBCS SCHEME

## Sixth Semester B.E. Degree Examination, July/August 2021 **VLSI** Design

Max. Marks:80

(04 Marks)

| Time: 3 hrs. Max. Marks:80 |          |                                                                                                                                                                       |                                         |  |  |

|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

|                            |          | Note: Answer any FIVE full questions.                                                                                                                                 |                                         |  |  |

| 1                          | a.<br>b. | Explain the nMOS enhancement mode transistor operation with a neat diagram. Explain the fabrication steps of CMOS P-well process with neat diagram and writ sequence. | (08 Marks)<br>te the mask<br>(08 Marks) |  |  |

|                            |          | · V                                                                                                                                                                   |                                         |  |  |

| 2                          | a.       | Obtain the DC transfer characteristics of a CMOS inverter and mark all the region                                                                                     |                                         |  |  |

|                            |          | the status of P-MOS and nMOS.                                                                                                                                         | (08 Marks)                              |  |  |

|                            | b.       | What are the advantages of BICMOS process over CMOS technology?                                                                                                       | (04 Marks)                              |  |  |

|                            | c.       |                                                                                                                                                                       |                                         |  |  |

|                            |          | i) Channel length modulation                                                                                                                                          | (04 Marks)                              |  |  |

|                            |          | ii) Noise margin.                                                                                                                                                     | (04 Marks)                              |  |  |

| 3                          | a.       | Explain λ based design rules with a neat diagram.                                                                                                                     | (08 Marks)                              |  |  |

|                            | b.       | - i i i i i i i i i i i i i i i i i i i                                                                                                                               | (08 Marks)                              |  |  |

|                            |          |                                                                                                                                                                       |                                         |  |  |

| 4                          | a.       | Derive the expression for sheet resistance.                                                                                                                           | (04 Marks)                              |  |  |

|                            | b.       | Derive an expression for the estimation of CMOS inverter delay.                                                                                                       | (08 Marks)                              |  |  |

|                            | c.       | Write a short note on super Buffers.                                                                                                                                  | (04 Marks)                              |  |  |

| _                          |          |                                                                                                                                                                       |                                         |  |  |

| 5                          | a.       | Find the scaling factors for :  i) Saturation current                                                                                                                 |                                         |  |  |

|                            |          | ii) Current density                                                                                                                                                   |                                         |  |  |

|                            |          | iii) Power dissipation/unit area                                                                                                                                      |                                         |  |  |

|                            |          | iv) Maximum operating frequency.                                                                                                                                      | (08 Marks)                              |  |  |

|                            | b.       | With a neat diagram, explain 4 × 4 barrel shifter.                                                                                                                    | (08 Marks)                              |  |  |

|                            |          |                                                                                                                                                                       | 1 43 17                                 |  |  |

| 6                          | a.       | Design a 4 bit ALU to implement addition subtraction, EX – OR, EX-NOR, OF                                                                                             | (08 Marks)                              |  |  |

|                            | h d      | operation.  Describe Manchester carry-chain.                                                                                                                          | (08 Marks)                              |  |  |

|                            | D.       | Describe Manchester carry-chain.                                                                                                                                      | (00 Marks)                              |  |  |

| 7                          | a.       | Discuss the architectural issues related to subsystem.                                                                                                                | (08 Marks)                              |  |  |

| 1070                       | b.       | Explain switch logic implementation of a 4 × 4 Four way multiplexer.                                                                                                  | (08 Marks)                              |  |  |

|                            |          |                                                                                                                                                                       |                                         |  |  |

| 8                          | a.       | Explain FPGA architecture.                                                                                                                                            | (08 Marks)                              |  |  |

|                            | b.       | Explain parity generator with basic block diagram and stick diagram.                                                                                                  | (08 Marks)                              |  |  |

|                            |          | Wanton it is in the life                                                                                                                                              | (00 ) (                                 |  |  |

| 9                          | a.       | Explain Pseudo-static RAM cell (NMOS) with schematic and stick diagram.                                                                                               | (08 Marks)                              |  |  |

|                            | b.       | Write a note on testability and testing.                                                                                                                              | (08 Marks)                              |  |  |

| 10                         |          | Explain three-transistor dynamic RAM cell with schematic and stick diagram.                                                                                           | (08 Marks)                              |  |  |

| 10                         | a.<br>b. |                                                                                                                                                                       | (04 Marks)                              |  |  |

|                            | U.       | Write about note on Duilt in Salf Test [DIST]                                                                                                                         | (04 Marks)                              |  |  |

c. Write short note on Built in Self Test [BIST].

Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

2. Any revealing of identification, appeal to evaluator and /or equations written eg. 42+8=50, will be treated as malpractice.

Time: 3 hrs.

## CBCS SCHEME

| USN |  |  |  |  |  |  |  |  |  |  | 15EC64 |

|-----|--|--|--|--|--|--|--|--|--|--|--------|

|-----|--|--|--|--|--|--|--|--|--|--|--------|

# Sixth Semester B.E. Degree Examination, July/August 2021 Computer Communication Networks

Computer Communication Networks

Note: Answer any FIVE full questions.

- 1 a. Explain different types of switched networks used in computer networks with relevant diagrams. (04 Marks)

- b. Explain layers of TCP/IP protocol suite with relevant diagram. (10 Marks)

- c. Assume a system uses five protocol layers. If the application program creates a message of 100 bytes and each layer adds a header of 10 bytes to the data unit, what is the efficiency of the system? (02 Marks)

- Explain with necessary diagram show ARP protocol finds link layer address of next node in a network.

(07 Marks)

- b. Explain the need for sequence number and acknowledgment numbers in stop-and-wait protocol with FSM and flow diagram. (07 Marks)

- c. Unstuff the following frame where payload in which 'E' is Escape byte, 'F' is the flag byte, and 'D' is a data byte other than an escape or a flag character.

### E E D E F D D E F E E D D D

(02 Marks)

Max. Marks:80

- 3 a. Explain behavior of three persistence methods with timing and flow diagram. (06 Marks)

- b. Show with frame exchange time diagram, how CSMA/CA solves hidden station problem.

(06 Marks)

- c. Assume that there are three active stations in a slotted ALOHA network: A, B and C. Each station generates a frame in a time slot with the corresponding probabilities  $P_A = 0.2$ ,  $P_B = 0.3$ ,  $P_C = 0.4$  respectively.

- i) What is the throughput of each station?

- ii) What is the throughput of the network?

(04 Marks)

- 4 a. Explain IEEE 802.3 frame format with neat diagram. (06 Marks)

- b. Explain with suitable diagram, 10 base 2 and 10 base 5 physical layer implementations in 10 Mbps Ethernet. (06 Marks)

- c. A network with one primary and four secondary station uses polling. The size of a data frame is 1000bytes. The size of the poll, ACK and NAK frames are 32 bytes each. Each station has 5 frames to send. How many total bytes are exchanged if there is no limitation on the number of frames a station can send in response to a poll?

(04 Marks)

- 5 a. Explain with neat diagram IEEE802.11 addressing mechanism. (06 Marks)

- b. Show with examples how redundant switches create loops in transparent switches. (06 Marks)

- c. In an 802.11 communication, the size of the payload is 1200 bytes. The station decides to fragment the frame into three fragments, each of 400 payload bytes. Answer the following questions:

- i) What would be the size of the data frame with fragmentation?

- ii) What is the size of each frame after fragmentation?

- iii) How many total bytes are sent after fragmentation?

- iv) How many extra bytes are sent because of fragmentation?

(04 Marks)

#### 15EC64

6 a. Explain with a neat diagram, three types of baseband layer formats.

(06 Marks)

b. Explain DHCP message format with neat diagram.

(04 Marks)

- c. An organization is granted the block 16.0.0.0/8. The administrator wants to create 500 fixed length subnets

- i) Find the subnet mask

- ii) Find the number of addresses in each subnet

- iii) Find the first and last address in subnet 1

- iv) Find the first and last address in subnet 500.

(06 Marks)

- 7 a. Show general formats of ICMP messages and explain query messages. (08 Marks)

- b. With neat diagram, mention three phases in remote host and mobile host communication.

(04 Marks)

- c. In a IPv4 datagram, the M bit is 0, the value of HLEN is 5, the value of total length is 200, and the offset value is 200, what is the number of the first byte and number of the last byte?

Is this the last fragment? (04 Marks)

- 8 a. Explain methods to overcome count-to-infinity problem considering two-node instability example with neat diagram. (06 Marks)

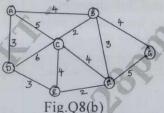

- b. Using Dijkstra's algorithm find the shortest path tree and the forwarding table for node 'A' in Fig.Q8(b).

(10 Marks)

- 9 a. Why window size in selective repeat protocol should be equal to  $2^{(m-1)}$ , prove your answer with flow diagram. (06 Marks)

- b. Design Go-Back-N sliding-window protocol for a network in which the bandwidth is 100Mbps and the average distance between the sender and receiver is 10,000km. Assume the average packet size is 100,000 bits and the propagation speed in the media is 2 × 10<sup>8</sup>m/s. Find the maximum size of the send and receive windows, the number of bits in the sequence number field (m), and an appropriate time-out value for the timer. (06 Marks)

- c. Show TCP segment format with neat diagram. (04 Marks)

- 10 a. Explain steps involved in three way handshaking during connection establishment in TCP protocol. (08 Marks)

- b. A client use UDP to send data to a server. The data length is 16 bytes. Calculate the efficiency of this transmission at the UDP level. (02 Marks)

- c. The following is part of a TCP header dump (contents) in hexadecimal format:

E2930017 00000001 00000000 500207FF

- i) What is the source port number?

- ii) What is the destination port number

- iii) What is sequence number?

- iv) What is the acknowledgment number?

- v) What is the length of the header?

- vi) What is the type of the segment?

- vii) What is the window size?

(06 Marks)